KATALOG IDT

|

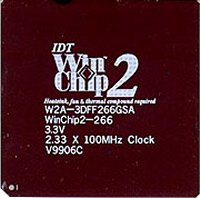

Procesor WinChip 2a

|

|

| Ogólnie o produkcie Szczegóły techniczne Podsumowanie | ||

Procesor WinChip 2a. Częstotliwość taktowania: 200, 233, 266, 300 MHz;

częstotliwość magistrali: 66 i 100 MHz; zasilanie pojedyncze: 3.3 lub 3.52

V; złącze: Super Socket 7; cache: L1 64 kB, L2 brak; technologia MMX i

3DNow! dla obsługi multimediów, zaawansowane zarządzanie energią.

|

||

|

|

||

|

|

||

WinChip 2a - do biura i do domu.

Dla wszechstronnych zastosowańWinChip 2a jako nowy członek rodziny procesorów firmy IDT wprowadza wysoką wydajność i technologię multimedialną MMX i 3DNow! do komputerów PC bazujących na oprogramowaniu x86 za wyjątkowo niską cenę. Dzięki kompatybilności procesora ze złączem Socket 7 (dostarczany w obudowie CPGA 296-pin) oraz jego niezwykle małym rozmiarom (rozmiar die zaledwie 58 mm2) obniża koszty produkcji nowych systemów oraz daje możliwość zwiększenia wydajności starych systemów poprzez wymianę jedynie procesora (nawet w przypadku płyt głównych obsługujących tylko pojedyncze zasilanie i przystosowanych do współpracy jedynie z procesorami Intel Pentium bez funkcji MMX).

Architektura

Sercem procesora, przystosowanego do osadzenia w gnieździe Socket 7,

jest bardzo wydajna jednostka RISC z pojedynczą, niedługą (4-pozycyjną)

kolejką rozkazów, z mechanizmem predykcji skoków. Innowacją jest tutaj

wczesne rozdzielenie danych i rozkazów, następujące już na poziomie ich

pobrania - procesor jest wyposażony w osobne pamięci cache dla instrukcji

i dla danych. Pobranie instrukcji następuje poprzez bufor TLB współpracujący

z pamięcią cache drugiego poziomu. Bufor ten zapewnia znaczące zwiększenie

"poziomu trafień" zarówno cache L2, jak i cache instrukcji. Współpraca

dwudrogowego mechanizmu skojarzeniowego cache L1 z czterodrogowym skojarzeniowym

buforem TLB to prawie dwukrotne zmniejszenie poziomu "chybień" L1. Bufor

TLB zawiera 128 wejść.

Pamięć podręczna i translator

Procesor posiada wbudowaną pamięć podręczną L1 o pojemności 64 kB (32

kB pamięci podręcznej dla rozkazów i 32 kB pamięci podręcznej dla danych).

Z pamięci podręcznej instrukcje są pobierane do translatora x86 na kod

RISC stanowiącego newralgiczny element procesora. Translator tłumaczy na

pojedyncze instrukcje wewnętrznego kodu RISC te rozkazy x86, które można

wykonać w pojedynczym cyklu, pozostałe realizowane są jako sekwencje mikroprogramowe.

Instrukcje RISC powstałe w translatorze przekazywane są, poprzez czteropozycyjną

kolejkę, do jednostki wykonawczej. Oczekujące w kolejce instrukcje są w

kolejnych fazach dekodowane, adresowane, wykonywane i zapisywane w postaci

wyników. Jednostka wykonawcza WinChipa to aż 6 równoległych jednostek -

stałoprzecinkowa ALU, zmiennoprzecinkowa FPU, dwie superskalarne jednostki

MMX oraz dwie jednostki 3DNow!. Dane dla operacji, jak również końcowe

wyniki, przekazywane są do pamięci RAM za pośrednictwem pamięci podręcznej

cache. Pomiędzy pamięciami cache a zewnętrzną szyną procesora zastosowano

4 rejestry buforowe (64-bitowe), które zapewniają kolejne zwiększenie płynności

przepływu danych.

Niezwykła plynność przepływu danych

Dla zapewnienia płynności przepływu danych, zapewnianej przez bardzo

sprawny system pamięci podręcznych; mimo niedługiej kolejki rozkazów, procesor

został wyposażony w 8-poziomowy sprzętowy stos skoków i powrotów, gwarantujący

znaczące usprawnienie obsługi przerwań. Przepływ danych jest dodatkowo

wspomagany funkcją predykcji skoków. Obsługa magistrali 100 Mhz zapewnia

także niezwykle szybki przepływ danych pomiędzy procesorem a pamięcią zewnętrzną.

Zasilanie tylko pojedynczym napięciem

WinChip ma jeszcze jedną zaletę - będąc przystosowanym do zasilania

pojedynczym napięciem 3.3 lub 3.52 V oraz będąc przystosowanym do złącza

Socket 7, stanowi propozycję procesora wyposażonego w rozszerzenie MMX

oraz 3DNow! dla wszystkich posiadaczy starszych płyt głównych z pojedynczym

napięciem zasilającym procesor (konstrukcje dla procesora P54 - Intel Pentium

bez funkcji MMX).

Kompatybilność

WinChip jest kompatybilny ze wszystkimi systemami operacyjnymi dla

procesorów x86, a więc DOS, Windows 3.1, Windows 95, Windows 98, Windows

NT, OS/2, Linux i wielu innymi. Współpracuje z płytami głównymi wyposażonymi

w chipsety firm Intel, ALi, SiS, Via i biosy firm Award, Phoenix i AMI.

Spełnia także wymogi kompatybilności z rokiem 2000.

Dane techniczne procesora WinChip 2a

ArchitekturaProcesor RISC, jednostki superskalarne, 6 równoległych jednostek wykonawczych.

Proces technologiczny

0.25 mikrona.

Rozmiar Die

58 mm2.

Częstotliwość taktowania

200, 233, 266, 300 MHz.

Częstotliwość magistrali

66 i 100 MHz (dla wersji z częstotliwością taktowania 266 i 300 MHz).

Pamięć podręczna

Dwupoziomowa. L1: 64 kB (32 kB cache danych i 32 KB cache instrukcji); L2: obsługa pamięci zewnętrznej na płycie głównej.

Koprocesor

Wbudowany, zgodny ze standardem IEEE-754, wykonujący także operacje 80-bitowe.

Multimedia

Technologia MMX (2 jednostki superskalarne) i 3DNow! (2 jednostki wykonawcze).

Cechy dodatkowe

Bufor danych TLB (128 wejść), prognozowanie skoków, 8-poziomowy sprzętowy stos skoków i powrotów, zaawansowane zarządzanie energią.

Obudowa

CPGA (296-pin).

Złącze

Super Socket 7.

Napięcia zasilające

Pojedyncze: 3.3 lub 3.52 V.

Kompatybilność sprzętowa

Kompatybilny z procesorami rodziny X86.

Kompatybilność programowa

DOS, Windows 3.1x, Windows 95, Windows 98,Windows NT 4.0, OS/2, Linux.

Temperatura pracy

od 0 do 65 st. C.

Gwarancja 1 rok

Windows jest znakiem handlowym Microsoft Corp. Wszystkie inne znaki firmowe i nazwy produktów są znakami handlowymi lub zastrzeżonymi znakami handlowymi odpowiednich firm. Specyfikacje przedstawione w tym dokumencie mogą bez uprzedzenia ulec zmianie. Emblemat Energy Star nie oznacza wyróżnienia przez EPA żadnej konkretnej firmy ani produktu.